第三章 指令级并行 (Instruction-Level Parallelism, ILP)

一、 基本概念

1. 指令级并行 (ILP):指在单个处理器内,通过硬件或软件技术,使得多条指令在执行阶段可以重叠进行,从而提高程序执行速度。其核心思想是挖掘和利用程序中指令之间潜在的并行性。

2. 关键度量:

* 并行度:平均每个时钟周期可以执行的指令数。

- 主要目标:使 CPI (Clock Cycles Per Instruction) 尽可能接近1甚至小于1。

- 限制ILP的因素:

- 数据相关 (Data Hazard):真数据相关(写后读,RAW)限制了指令的执行顺序。

- 名字相关 (Name Hazard):反相关(写后写,WAW)和输出相关(读后写,WAR),可通过寄存器重命名解决。

- 控制相关 (Control Hazard):由分支指令引起,影响指令的取指顺序。

- 结构冲突 (Structural Hazard):硬件资源冲突。

二、 基于硬件的动态调度技术

- 记分板算法 (Scoreboarding)

- 目标:在保持数据流和异常行为的前提下,允许指令乱序执行(Out-of-Order Execution)。

- 核心思想:中央控制器(记分板)跟踪所有指令的状态、数据相关性和资源使用情况。指令在译码后进入记分板,当操作数就绪且功能单元可用时,记分板才发射该指令执行。

- 执行阶段:分为4段:

- 发射 (Issue):检查结构冲突与WAW相关。

- 读操作数 (Read Operands):等待数据相关消除(即源操作数就绪)。

- 执行 (Execution):在功能单元中计算。

- 写回 (Write Back):结果写回寄存器。

- 缺点:检测和解决所有相关,硬件复杂;无法处理WAR和WAW相关(通过停顿解决,影响效率)。

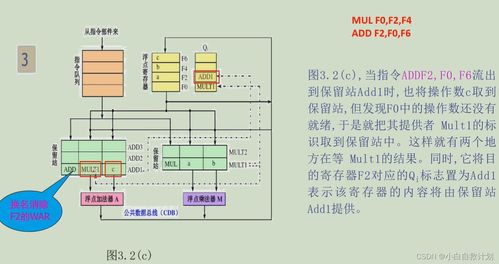

- Tomasulo算法

- 核心改进:

- 分布式控制:通过保留站(Reservation Station)进行指令调度,而非中央记分板。

- 寄存器重命名:使用保留站和公共数据总线(CDB)实现,彻底消除WAR和WAW相关。

- 前瞻执行:为处理控制相关(分支)奠定基础。

- 主要部件与流程:

- 保留站:缓存已发射但未执行的指令及其操作数(或指向操作数的指针)。

- 公共数据总线:广播结果,实现数据前递(Forwarding)。

- 流程:发射 -> 执行 -> 写回。在“发射”阶段,若操作数未就绪,则从寄存器或CDB获取“标签”,实现寄存器重命名。

- 优势:能高效处理数据相关,支持乱序执行,为后续的分支预测和推测执行提供了硬件基础。

三、 基于硬件的分支预测与推测执行

- 分支预测 (Branch Prediction)

- 动机:减少控制相关带来的流水线停顿。

- 静态分支预测:编译时确定,如“总是预测不跳转”、“向后跳转预测跳转”等。简单但准确率有限。

- 动态分支预测:运行时根据历史信息进行预测。

- 分支历史表 (BHT):使用分支指令地址的低位索引一个表,表中记录上次执行的结果(跳转/不跳转)。

- 两位饱和计数器:提高预测准确性,需两次预测错误才会改变预测方向,具有良好的稳定性。

- 分支目标缓冲器 (BTB):缓存预测跳转的分支指令的目标地址,可在取指阶段直接提供目标指令地址。

- 相关分支预测器 (如两位局部/全局历史预测器):利用分支之间的相关性(模式)进行更精确的预测。

- 推测执行 (Speculative Execution)

- 概念:基于分支预测的结果,在分支指令结果确定之前,提前执行预测路径上的指令。

- 硬件支持(结合Tomasulo算法):

- 重排序缓冲器 (ROB):核心组件。按程序顺序缓存所有推测执行的指令及其结果。

- 流程:指令按序发射到ROB和保留站,乱序执行,但结果先写入ROB,并不立即更新寄存器。只有当指令在ROB中变为最旧的、且非推测状态时,才按序提交结果到寄存器或内存。

- 异常处理:在推测执行期间发生的异常被记录在ROB中,只有在该指令提交时才真正处理,保证了异常行为的精确性。

- 错误预测恢复:当分支预测错误时,清空该分支之后的所有推测执行指令(清空ROB和保留站相关项),并从正确路径重新取指。

四、 基于软件的静态调度技术(由编译器完成)

- 循环展开 (Loop Unrolling)

- 将循环体复制多次,减少循环控制指令(如分支、自增)的开销,为编译器调度创造更多指令,以填充延迟槽。

- 需注意寄存器压力增加和代码膨胀问题。

- 指令调度 (Instruction Scheduling)

- 编译器通过调整指令顺序,尽可能分离存在数据相关的指令,以填充因数据相关或功能单元延迟导致的流水线气泡。

- 常用方法:静态调度、软流水线 (Software Pipelining) 等。

- 静态多发射处理器与VLIW

- 静态多发射:处理器每个时钟周期发射固定数量的指令包,依赖编译器在编译时挖掘ILP,并将指令打包,硬件相对简单。

- 超长指令字 (VLIW):静态多发射的典型代表。一条“超长指令”包含多个独立操作字段,编译器负责调度和打包,硬件无需复杂的动态调度逻辑。

- 挑战:对编译器要求极高;二进制代码兼容性差;难以处理缓存缺失等动态事件。

五、 多发射处理器

1. 超标量处理器 (Superscalar):每个时钟周期动态发射可变数量的指令(如1-8条),依赖硬件(如Tomasulo)进行动态调度、相关检测和乱序执行。这是现代通用CPU的主流技术。

2. 超流水线处理器 (Superpipelining):将流水线划分成更多、更细的阶段,通过提高主频来提升性能,属于时间并行。常与超标量技术结合使用。

本章小结

指令级并行是提升单处理器性能的核心技术。主要途径包括:

- 硬件动态方法:通过记分板、Tomasulo算法实现乱序执行;结合分支预测和推测执行(ROB)克服控制相关。

- 软件静态方法:通过编译器进行循环展开、指令调度,服务于静态多发射/VLIW架构。

- 现代高性能处理器(如Intel/AMD的CPU)普遍采用动态调度的超标量结构,并结合强大的分支预测和推测执行技术,以挖掘程序中的指令级并行。